<Direto ao Ponto 14> Arquiteturas de Computador Alternativas

- #Informática Básica

Artigos desta série: ( < ) Anterior | Índice | Seguinte ( > )

Olá, dev!

Este é mais um artigo da série DIRETO AO PONTO, que eu estou escrevendo para a DIO. Ele vai tratar das arquiteturas de computador criadas para resolver os problemas encontrados na arquitetura de von Neuman.

Também serão tratadas outras formas de arquiteturas específicas, que surgiram após os avanços da tecnologia.

Sumário

1. Introdução

2. A Arquitetura de von Neumann (resumo)

3. Arquiteturas alternativas

4. Considerações finais

5. Referências

1 – Introdução

A série DIRETO AO PONTO enfoca artigos sobre conhecimentos básicos da programação e é voltada, principalmente, para os iniciantes.

Neste novo artigo, eu vou apresentar novas arquiteturas de computador, focando em arquiteturas alternativas àquela mais comum, de von Neumann, base dos computadores atuais.

Também serão tratadas outras formas de arquitetura diferenciadas que surgiram recentemente, após grandes avanços da tecnologia.

2 – A Arquitetura básica de um computador

A arquitetura dos computadores atuais segue a arquitetura de von Neumann, criada por John von Neumann, em 1945.

Segundo (Carter, 2022), praticamente todos os projetos de computadores modernos são baseados na arquitetura de von Neumann, que estabelece 3 conceitos principais:

· Dados e instruções são armazenados em uma única memória de leitura e escrita;

· O conteúdo dessa memória é endereçável pela localização, sem considerar o tipo de dados contido ali;

· A execução ocorre em um padrão sequencial de uma instrução para a seguinte, a não ser que isso seja modificado explicitamente.

A figura a seguir ilustra esta arquitetura, que hoje representa a estrutura básica de um processador moderno:

3 – Arquiteturas alternativas

Segundo (Ledin, 2022), a decisão conceitual de usar uma única região de memória para todo o código e os dados simplificou o projeto e a construção das primeiras gerações de processadores e computadores, facilitando a vida dos programadores e dos projetistas de circuitos.

No entanto, o compartilhamento de memória entre programas e dados apresenta algumas dificuldades:

• Limitação de desempenho do sistema - esta arquitetura requer vários ciclos de memória para recuperar uma instrução do processador e acessar os dados necessários. Este problema é conhecido como o gargalo de von Neumann. Isso pode ser mitigado significativamente com o uso de memórias cache para instruções e dados de programas, mas se os códigos e dados excederem o tamanho da memória cache, o benefício do seu uso será bem reduzido.

• Criação de uma brecha de segurança - programadores maliciosos podem se aproveitar da memória compartilhada e armazenar sequências de instruções na memória como se fossem “dados”, direcionando o processador para executar essas instruções. Essa vulnerabilidade é conhecida como estouro do buffer (“Buffer Overflow”).

Esta é uma falha muito comum em ferramentas de software amplamente utilizadas, como sistemas operacionais, servidores web e bancos de dados, tendo sido explorada há anos por hackers.

Fabricantes de processadores e desenvolvedores de sistemas operacionais implementaram uma variedade de recursos para combater este tipo de ataque, com correções eficazes, até certo ponto.

Por causa destas limitações importantes, foram propostas algumas arquiteturas alternativas, que procuram evitar, ou minimizar, estes problemas vistos na arquitetura de von Neumann.

A arquitetura de Harvard

Esta arquitetura foi originalmente implementada no computador Harvard Mark I, em 1944. Uma arquitetura de Harvard estrita usa espaços de endereçamento e barramentos de memória completamente separados para armazenar instruções de programa e dados.

Ela configuração permite o acesso simultâneo a instruções e dados, implementando uma forma de paralelismo. Além disso, a melhoria ocorre à custa da duplicação do número de linhas de endereço, linhas de dados e sinais de controle, que precisam ser implementados no processador para acessar as duas regiões de memória.

Potencialmente, esta arquitetura fornece um nível de desempenho mais alto, ao paralelizar acessos a instruções e dados, além de remover todos os problemas de segurança associados ao “buffer overflow”.

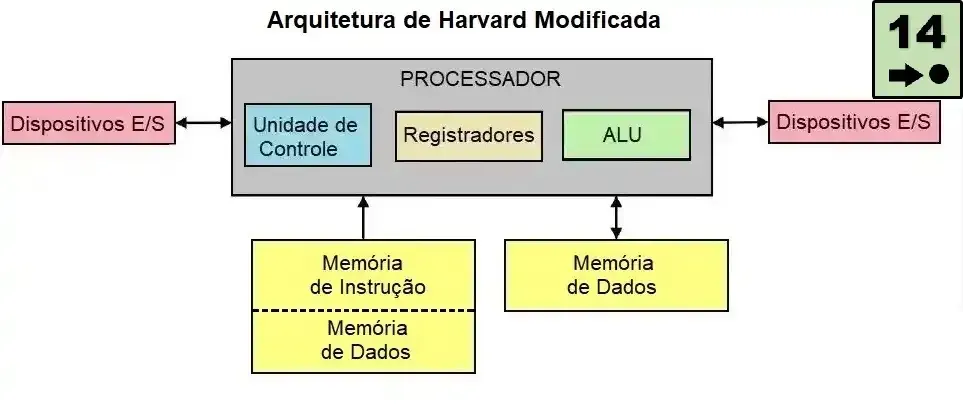

O diagrama a seguir mostra o layout de um processador implementando a arquitetura de Harvard:

Na prática, uma arquitetura de Harvard estrita raramente é usada em computadores modernos. Diversas variantes desta arquitetura são comumente empregadas, chamadas de arquiteturas de Harvard modificadas.

A arquitetura de Harvard modificada

Em geral, computadores projetados assim têm algum grau de separação entre instruções do programa e dados, o que já reduz os efeitos do gargalo de von Neumann e mitiga os problemas de segurança discutidos, mas essa separação raramente é absoluta.

O diagrama a seguir mostra uma arquitetura Harvard modificada, que é utilizada por muitos computadores atuais:

De acordo com (Ledin, 2022), os computadores modernos utilizam arquiteturas baseadas nas características dos seus processadores, com as mais comuns listadas a seguir:

· x86 (Intel e AMD),

· x64 (Intel e AMD),

· ARM de 32 bits;

· ARM de 64 bits.

Em relação ao design do processador, as arquiteturas x86 e x64 seguem, principalmente, uma abordagem CISC (“Complex Instruction Set Computer”, ou Computador com um Conjunto Complexo de Instruções), enquanto as arquiteturas ARM implementam processadores RISC (“Reduced Instruction Set Computer”, ou Computador com Conjunto Reduzido de Instruções).

Atualmente, foi estabelecida uma nova especificação da arquitetura RISC (RISC V), que tem como objetivo:

· Ser adequada para uso em um largo espectro de aplicações, desde dispositivos embarcados de baixíssima potência até servidores multiprocessados de alto desempenho para a nuvem (“cloud”);

· Ser gratuita para uso por qualquer um, para qualquer aplicação, contrastando com todos os outros processadores disponíveis comercialmente, que têm sua propriedade intelectual cuidadosamente guardada pelos fabricantes.

Algumas aplicações relevantes com processadores RISC-V já começaram a fazer avanços significativos:

· Inteligência Artificial e Machine Learning;

· Sistemas embarcados;

· Computação de escala extrema;

· Processamento de potência ultra baixa;

· Processamento de borda de IoT.

Saindo um pouco da arquitetura original de von Neumann, existem outras arquiteturas para implementações no mundo real de sistemas de computação modernos, de alto desempenho ou de segurança extrema, que precisam ser adaptadas às necessidades específicas do usuário, como:

· Smartphones;

· computadores pessoais voltados para jogos (alto desempenho);

· computação em escala para implementação de warehouses;

· redes neurais;

· blockchain,

· mineração de bitcoin,

· veículos autônomos.

Finalmente, estão surgindo tecnologias potencialmente disruptivas que podem alterar o caminho das futuras arquiteturas de computadores, como a computação quântica, por exemplo.

4 – Considerações finais

Este é mais um artigo da série DIRETO AO PONTO, que eu estou escrevendo para a DIO.

Ele tratou de outros tipos de arquiteturas, surgidas para tentar resolver os problemas principais da arquitetura de von Neumann, como o gargalo de von Neumann e problemas de segurança, consequências da decisão de se usar o mesmo espaço de memória para instruções do programa e dados.

Também foram listadas aplicações modernas que exigem arquiteturas que suportem mais desempenho ou mais segurança, como smartphones, jogos digitais, blockchain e veículos autônomos, bem como aplicações bem disruptivas, como a computação quântica.

5 – Referências

[1] CARTER Nicholas, Schaum’s Outline of Computer Architecture. McGraw-Hill, 2002.

[2] LEDIN, Jim. Modern Computer Architecture and Organization. 2nd Edition. Packt Publishing, 2022.

Artigos desta série: ( < ) Anterior | Índice | Seguinte ( > )